Low-Power System-on-Chip Design

Lecture Overview

|

With technological advances that allow us to integrate complete multi-processor systems on a single die, Systems-on-Chip (SoCs) are at the core of most embedded computing and consumer devices, such as cell phones, media players and automotive, aerospace or medical electronics. This course will provide an understanding of the concepts, issues, and process of designing highly integrated SoCs following systematic hardware/software co-design & co-verification principles, especially about the low-power design techniques and methodologies for the light weighted realization of the long-term operative embedded systems. |

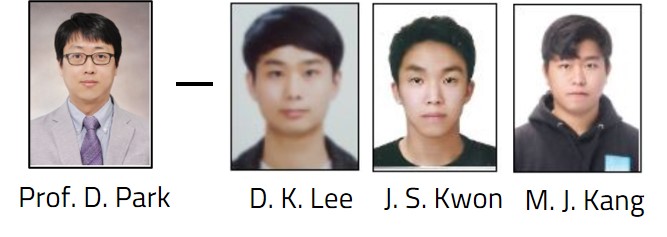

Prof. Daejin Park introduces basic fundamentals for the given lectures during 1 hour, then practice items by examples will be given. Mr. Dongkyu Lee will explain the experiment in details. Mr. Kwon and Mr. Kang are ready to assist the students during lab time. Students can ask any questions to these lecture assistants (TAs) directly or through lms web site.

Prof. Daejin Park introduces basic fundamentals for the given lectures during 1 hour, then practice items by examples will be given. Mr. Dongkyu Lee will explain the experiment in details. Mr. Kwon and Mr. Kang are ready to assist the students during lab time. Students can ask any questions to these lecture assistants (TAs) directly or through lms web site.

Assignments

This lecture is experiment class. We cover only small parts of boring theory. Everything you have to do is to write your codes by yourself. All students have to do the programming problems themselves within 3 hours. The every on-the-live test will be given during the lecture.

Grading Criteria

Mid test 25%, final test 35% are evaluated by on-site programming and demonstration method. The lab during the every lecture is evaluated everyone, for 20% credit. The report is also given for 20% record. 5%record will be evaluated regarding to the safety preliminary class.

Lecture Timeline

The following is a brief time schedule during one semester. Please contact us to get the detailed lecture information including lecture slides. The registered students can get the lecture slides from KNU lecture management systems (lms).

Understanding of Power Consumption in CMOS VLSI

Toggle Minimization-based Low-Power Design Techniques

Clock Network-Optimization for Dynamic Current Reduction

Signal Processing-based Operating Time Reduction

Event-Driven Signal Processing-based Low-Power System Design

Size and Power Consumption Reduction in Memory Circuit

Designing Low-Power Calculation Unit including ALU

Asynchronous Circuit Design based on Multi-Clock Domains

Buffered Design Techniques for Isolated Power and Clock Domains

Dynamic Voltage and Frequency Scaling Method

Circuit Design Techniques for Power-Gating and Clock-Gating

Circuit Optimization Techniques for Asynchronous Logics

Toggle Filtering-based Active Time Minimization for Efficient Power Mode