Yujeong Son (Undergraduate Student)

|

Undergraduate Student (B.S), Embedded System-on-Chip Integrator |

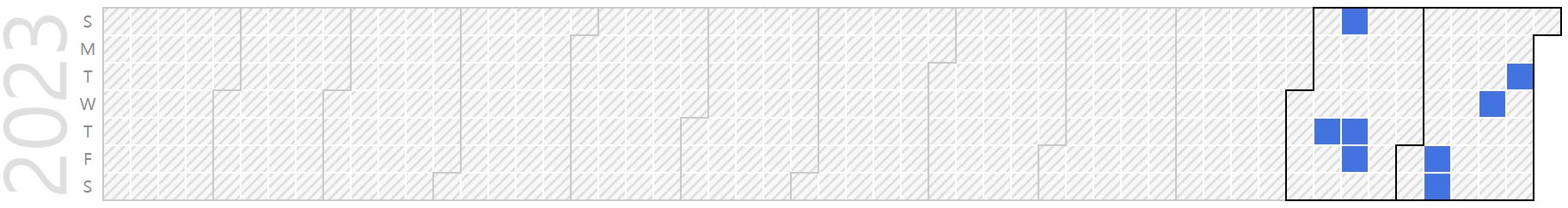

Repository Commit History

|

Introduction

Full Bio Sketch

Mr. Son is currently doing his undergraduate degree in School of Electronic Engineering at Kyungpook National University, Daegu, Republic of Korea. His research interests include a system with robustness against errors, especially on look-ahead instruction fetch protection on pipeline stage using error correction unit. In the future, he will focus on various methods reducing power consumption while maintaining robustness in digital signal processors.

Research Topic

yjson_topic1.jpg In embedded systems, the programs and data processed by chips are progressively increasing in size. Consequently, errors during data transmission due to noise or various factors are becoming more frequent. Errors in bits may only be a minor inconvenience for users, but in certain systems with military purposes or vehicles, for example, they can lead to critical issues. Methods for addressing these errors include requesting data to be resent to the processor or introducing redundancy bits to enhance data reliability. However, a commonly employed modern approach is the use of ECC (error-correcting code) algorithms. ECC algorithms not only detect errors but also sometimes enable immediate error correction.

yjson_topic2.jpg He has implemented a 5-stage pipelined processor with an ECU capable of correcting one error and detecting two errors. Through testing, it was confirmed that in the event of a single error, the processor autonomously recovers from the error. However, when two or more errors occur, signals are conveyed to the processor, enabling it to either re-execute from the point of error occurrence or utilize alternate strategies. Such error resilient processors hold the potential for applications in real-time data processing domains like automotive systems, where reliability is demanded.

Publications

Conference Publications (Intl. 1)

Yujeong Son and Daejin Park. FPGA Implementation of On-chip Instruction Fetch Protection on Pipeline Stage Using Error Correction Unit In 2024 International Conference on Artificial Intelligence in Information and Communication (ICAIIC 2024), 2024.

Participation in International Conference

IEEE ICMU 2023, Kyoto, Japan

IEEE ICAIIC 2023, Osaka, Japan

Last Updated, 2023.11.26