Nayoung Kwon (Integrated Ph.D. Student)

|

Ph.D Candidate, VLSI Design Accelerator |

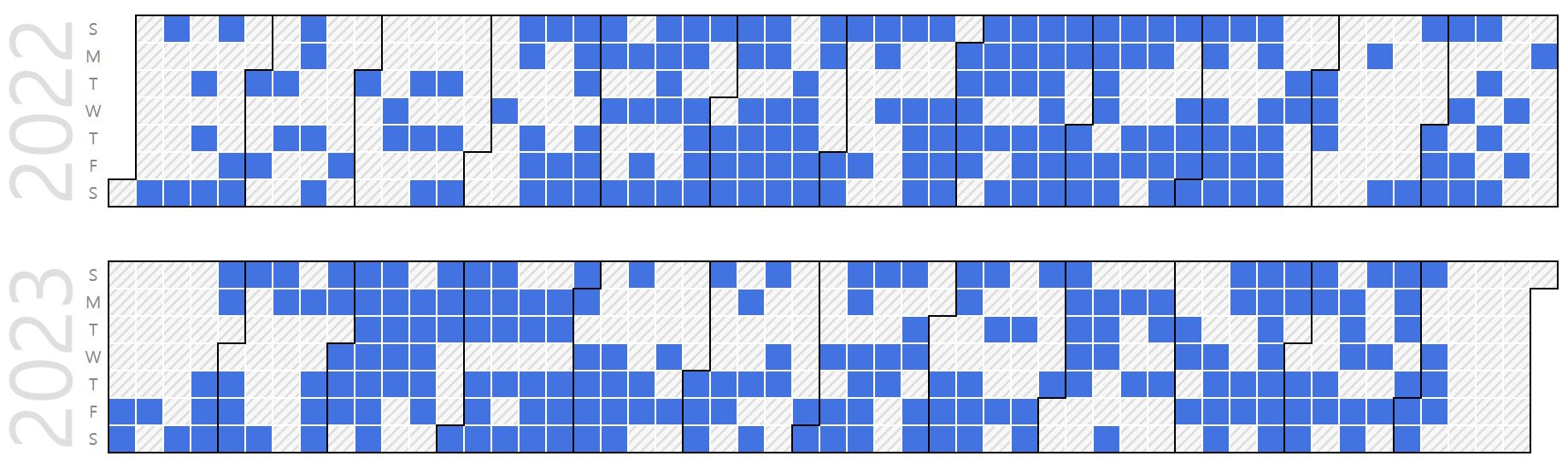

Repository Commit History

|

Introduction

Full Bio Sketch

Ms. Kwon received her B.S. Degree in Electronics Engineering at Kyungpook National University, Daegu, Korea in 2023. Her research interests include Accelerating VLSI system Algorithm and machine learning based design automation. Her research was focused on efficient clock tree architecture using CTS (Clock Tree Synthesis) buffer insertion algorithm and CTS process automation in Verilog RTL stage. She currently conducts research about to robust algorithm to improve performance, power, area (PPA) on CTS and placement and route (P&R) process. She also researches new CTS algorithm through low power simulation using UPF.

Research Topic

nykwon_topic1.jpg CTS is the process of connecting the clocks to all clock pin of sequential circuits by using inverters/buffers in order to balance the skew and to minimize the insertion delay. Her research is focused on Low-power and Fast speed Buffer insertion on CTS process. Currently, CTS process automation is being studied to simplify and accurate circuit analysis. In RTL Stage, arbitrary circuit is tracked to calculate automatically gate delay by Verilog parser. In next stage, the circuit in RTL stage is reflected buffer insertion through feedback CTS process and visualization by Graphviz tool.

nykwon_topic2.jpg Micro controller unit (MCU) are mainly used in low power devices, which use limited energy sources such as batteries, energy harvesting, and wireless communications. Therefore, reducing the operating power of the MCU is important to improve energy efficiency by extending battery life or minimizing energy consumption. The MCU is one of the chip designs composed of digital integrated circuits. The clock signal is important element to the MCU. The clock tree, which consists of the clock signal is directly related to MCU low power operation and performance improvement. Also, chip verification process is important role to improve performance of overall system and reliability to the MCU. However, as the degree of integration of chips, the chip verification process increases complexity and time-consumption to process many data. Currently, many users dependent on licensed electronic design automatic (EDA) tools to ensure high accuracy, minimizing errors in circuit design and improving reliability. The use of licensed EDA tool puts a burden on users including high costs, limited license, difficulty in customization, slow speed, etc. An effective approach to avoid problems by using licensed EDA tools proceeds verification that is unrestricted license and customization for possible using only a register transfer level (RTL) source. In this paper, we propose to predict roughly pre-estimated CTS results using an RTL source in which temporary logic using random buffer insertion is placed before the route process. This paper contributes to reducing MCU operating power and hardware area by performing optimized CTS and minimizing resources according to the RTL structure to be designed.

Publications

Journal Publications (KCI 1, SCI 1)

Nayoung Kwon and Daejin Park. Lightweighted CTS Preconstruction Techniques for Checking Clock Tree Synthesizable Paths in RTL Design Time (KCI) Journal of the Korea Institute of Information and Communication Engineering, 2022.

Nayoung Kwon and Daejin Park. Shallow Clock Tree Pre-estimation for Designing Clock Tree Synthesizable Verilog RTLs (SCI) Electronics, 2023.

Conference Publications (Intl. 4)

Nayoung Kwon and Daejin Park. Lightweight Buffer Insertion for Clock Tree Synthesis Visualization In 2022 International Conference on Electronics, Information, and Communication (ICEIC), 2022.

Nayoung Kwon and Daejin Park. Lightweighted CTS Preconstruction Techniques for Checking Clock Tree Synthesizable Paths in RTL Design Time In IEEE ISOCC 2022, 2022.

Myeongjin Kang, Nayoung Kwon, Seungmin Lee, and Daejin Park. Fast Bit Inversion Vulnerability Pre-estimation using Tcl and UPF in RTL Simulation Runtime In IEEE International Conference on ICT Convergence (ICTC 2023), 2023.

Nayoung Kwon and Daejin Park. Lightweighted Shallow CTS Techniques for Checking Clock Tree Synthesizable Paths and Optimizing Clock Tree in RTL Design Time In IEEE International Conference on ICT Convergence (ICTC 2023), 2023.

Participation in International Conference

IEEE ICEIC 2022, Jeju, Korea

IEEE ISOCC 2022, Gangreung, Korea

IEEE Micro 2022, Chicago, USA

IEEE ASP-DAC 2023, Tokyo, Japan

IEEE COOLChips 2023, Tokyo, Japan

IEEE ICTC 2023, Jeju, Korea

Last Updated, 2023.10.16